EtherCAT主站芯片方案 (virtual ASSP)

概述

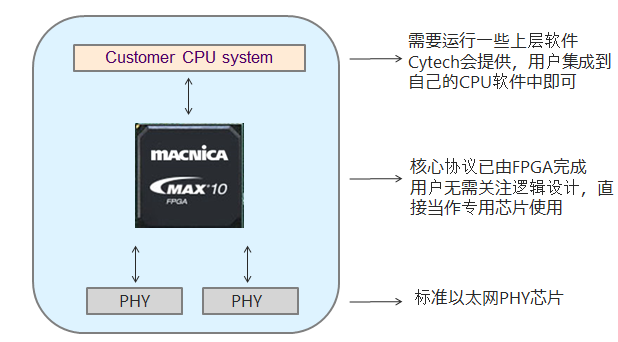

EtherCAT商业主站和开源主站,都是使用软件的方法实现主站功能,主站的性能很大程度上取决于PC的性能和操作系统的实时性。而骏龙科技将EtherCAT的协议层用FPGA逻辑实现,预先编程好,客户只需当作专用芯片使用。

EtherCAT Master ASSP芯片实现了标准的EtherCAT主站协议,采用标准的通用并行总线接口,可以连接任何CPU,并对芯片进行控制。支持ARM处理器或者x86处理器平台。提供参考软件代码,API函数,XML文件初始化系统等软件。可用于任何标准的 EtherCAT 电机、IO设备的控制。

特点

- 支持ARM处理器上裸机程序运行EtherCAT主站,无需操作系统;

- 支持x86处理器,PCIe接口,提供Linux(withXenomai实时内核)下的驱动和应用程序的参考代码;

- 友的系统调试界面;

- CPU负担小,无论高端或低端处理器,都能快速实现高实时性能的EtherCAT主站通信;

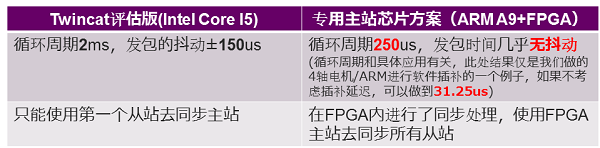

- 主站与从站间的同步性能强,同步时间的抖动远小于1us(4轴实测50ns);

- 循环周期短,可以轻松实现31.25us的通信周期(可实现4轴62.5us的循环周期);

- 通过XML文件轻松配置系统,可接从站数量多

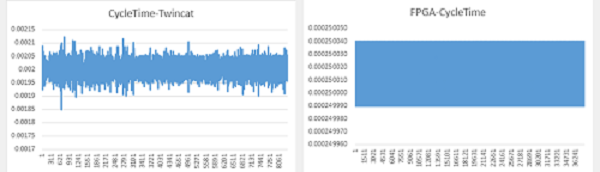

性能对比

欢迎有兴趣的客户联系骏龙科技各地办事处了解详情,或发邮件至 stonemao@macnica.com, 也可以关注微信号后直接微信留言。骏龙科技网站也可以留言。

骏龙科技微信号:

更多資訊: