EtherCAT Master ASSP Chip Solution

Overview

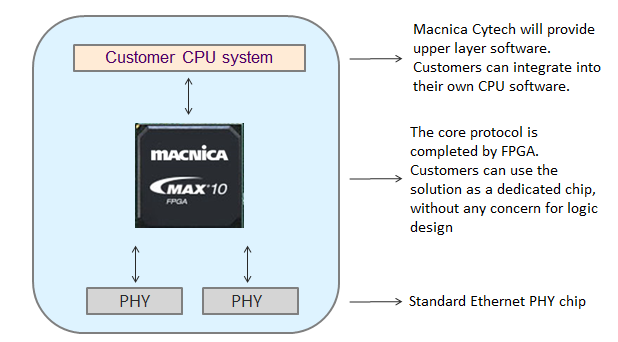

Both commercial and open-source EtherCAT masters apply software to achieve the function of master station. To a large extent, the master’s function depends on the performance on PC and the real-time operating system. Macnica Cytech implements EtherCAT’s protocol layer by FPGA logic, through pre-programming. Customers could use it as a dedicated chip.

The EtherCAT Master ASSP Chip practices the standard EtherCAT master protocol. It adopts generic

parallel bus interface to connect whichever CPU, and control the chip. It supports ARM processors or x86 processing platform. Macnica Cytech could provide software’s reference code, API function, and software for XML document initialization system etc. This solution could be applied to control standard EtherCAT motors and IO equipment.

Characteristics

- Supports the bare-metal programming for EtherCAT master on ARM processor; no operating system is required

- Supports x86 processor and PCIe connector; reference code of Linux (with Xenomai real-time kernel) driver and application is provided

- User-friendly system debug window

- Small burden on CPU; real-time EtherCAT master communication could be quickly achieved, no matter with high-end or low-end processors

- Strong synchronization between master and slave; the jitter of synchronization time is smaller than 1us (4-axis measurement 50ns)

- Short cycle; a 31.25us communication cycle could be achieved easily (4-axis 62.5us cycle could be achieved)

- Various slave stations could be connected and configured through XML document configuration system

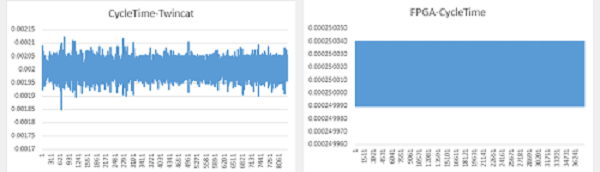

Comparison

| Twincat Evaluation Version (Intel Core I5) | EtherCAT Master ASSP Chip Solution (ARM-A9+FPGA) |

| 2ms cycle, ±150us jitter on packet time | 250us cycle, almost no jitter on packet time (cycle and application are related; the result here is based on an example which our team conducted 4-axis motor with ARM achieving software interpolation; if the delay of interpolation is not considered, 31.25us could be achieved) |

| The master synchronizes with the first slave | Synchronization completed in FPGA; FPGA master is used to synchronize with all slaves |

For details of Macnica Cytech’s products and solutions, please contact the company’s regional offices, or send emails to stonemao@macnica.com. You may also follow Macnica Cytech’s WeChat official account to leave messages, or leave messages through the Macnica Cytech’s website.

Macnica Cytech's WeChat official account:

For more information: